EETIMES 刊登 汎銓科技技術文章 全球首家 完整解析 三星 3奈米GAA 製程結構

![]() 2024.10.16

2024.10.16

新聞公告

新聞公告

GAA架構並不會是電晶體架構的終點。但因應日趨複雜的製程架構、多樣的材料以及原子等級的結構尺寸,材料分析也必須與時俱進...

在半導體產業,透過在製程中降低晶片內電晶體的漏電、減少耗能,可說是一種實踐環境永續的具體作法,如何有效降低漏電,成為多年來電晶體架構革命性演進的主要驅動力。

以平面式電晶體架構來看,通道長度由於製程技術隨著摩爾定律越縮越短,當低於數十奈米(nm)時,短通道效應所導致的漏電就越來越嚴重,因此在2000年有了3D鰭式電晶體(FinFET)原型架構的誕生,並於2011-2012年開始實現商業化量產。

鰭式電晶體架構是將原本平面的源極(Source)和汲極(Drain)轉變成立體結構,讓閘極(Gate)三面包覆通道,使得閘極與通道之間的接觸面積變大,提升閘極控制電子的能力,因而可以降低漏電。但隨著製程技術不斷的推進,通道長度持續縮減,研發工程師很快地理解到,當閘極與通道之間的接觸面積縮小到某一程度後,漏電將再度成為一個必須面對的課題。

因此,在鰭式電晶體商業化生產幾年後,各研究單位與重要的電機電子工程師學會會議就開始醞釀與討論新一代電晶體架構的研發技術藍圖,雖然最終各家對於新一代電晶體架構的名稱莫衷一是,但其核心的概念都在於增加閘極與通道之間的接觸面積,以進一步提升閘極控制電子的能力。

由於先前鰭式架構的閘極是三面包覆通道,為了在縮減通道長度的狀況下,增加閘極控制電子的能力,新一代的架構是讓閘極四面整個包覆通道,稱為環繞式閘極(gate-all-around;GAA)電晶體架構。全球主要先進製程的晶圓代工廠都已經揭示採用GAA架構的時程,這當中又以韓國三星電子(Samsung)最為積極,率先在3nm製程節點採用GAA架構,並於2022年正式投產。

第一個採用三星GAA架構製程的不是一般消費性產品,而是挖礦專用的ASIC晶片Whatsminer M565++ (MicroBT),與消費性產品最大的不同是Whatsminer M565++晶片僅有邏輯單元,並沒有記憶體單元,雖然贏得了全球第一個量產GAA電晶體的矚目眼光,但顯然在製程良率上的挑戰仍大。

經過一年多的技術提升與優化,三星第一個一般消費性產品採用GAA架構製程終於在2024年發表,該產品是用於三星Galaxy Watch 7的處理器Exynos W1000,採用的製程技術為三星在2023年推出的第二代GAA架構3nm製程節點。

雖然GAA電晶體有較佳的效能,但相較於發展已相當多年、製程相對成熟的FinFET製程,GAA FET製程更為複雜且遭遇的技術挑戰困難許多,為了達到製程與電晶體效能的最佳化,製程研發上勢必導入不少技術創新。汎銓科技(MSScorps)利用高空間解析的穿透式電子顯微鏡(TEM)搭配能量色散X射線光譜(Energy dispersive X-ray spectroscopy;EDS)帶你一窺三星GAA FET的製程細節。

此次研究的產品是用於三星Galaxy Watch 7的處理器Exynos W1000,所採用的製程技術為三星第二代GAA架構3nm製程節點,由三星官網公開的資訊,新的3nm製程GAA架構在單核心與多核心的效能上比前一代(仍是FinFET架構)分別提升了3.4與3.7倍。

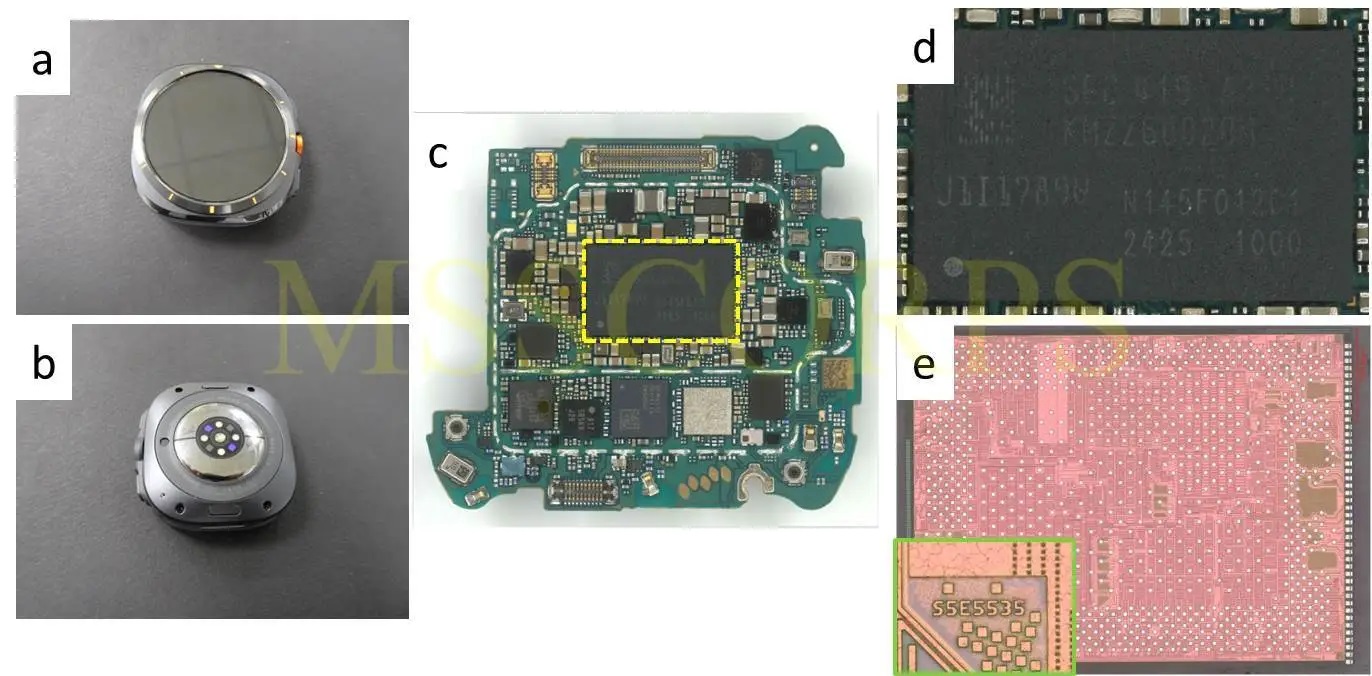

圖1a與圖1b為三星Galaxy Watch 7的正面與背面照,拆開手錶後可以看到主要的PCB版(圖1c),板子上由黃色虛線方框標示的就是本次分析的主角Exynos W1000,其表面雷射刻號可以由圖1d清楚看到,在去除封裝體後,則可以看到整個晶片的樣貌與標誌編號。

圖1:(a & b) 三星Galaxy Watch 7的正面與背面照;(c) PCB主板光學顯微鏡圖,Exynos W1000由黃色虛線方框標示;(d) Exynos W1000特寫光學顯微鏡圖;(e) Exynos W1000去除封裝體後光學顯微鏡圖,晶片標誌編號為S5E5535。

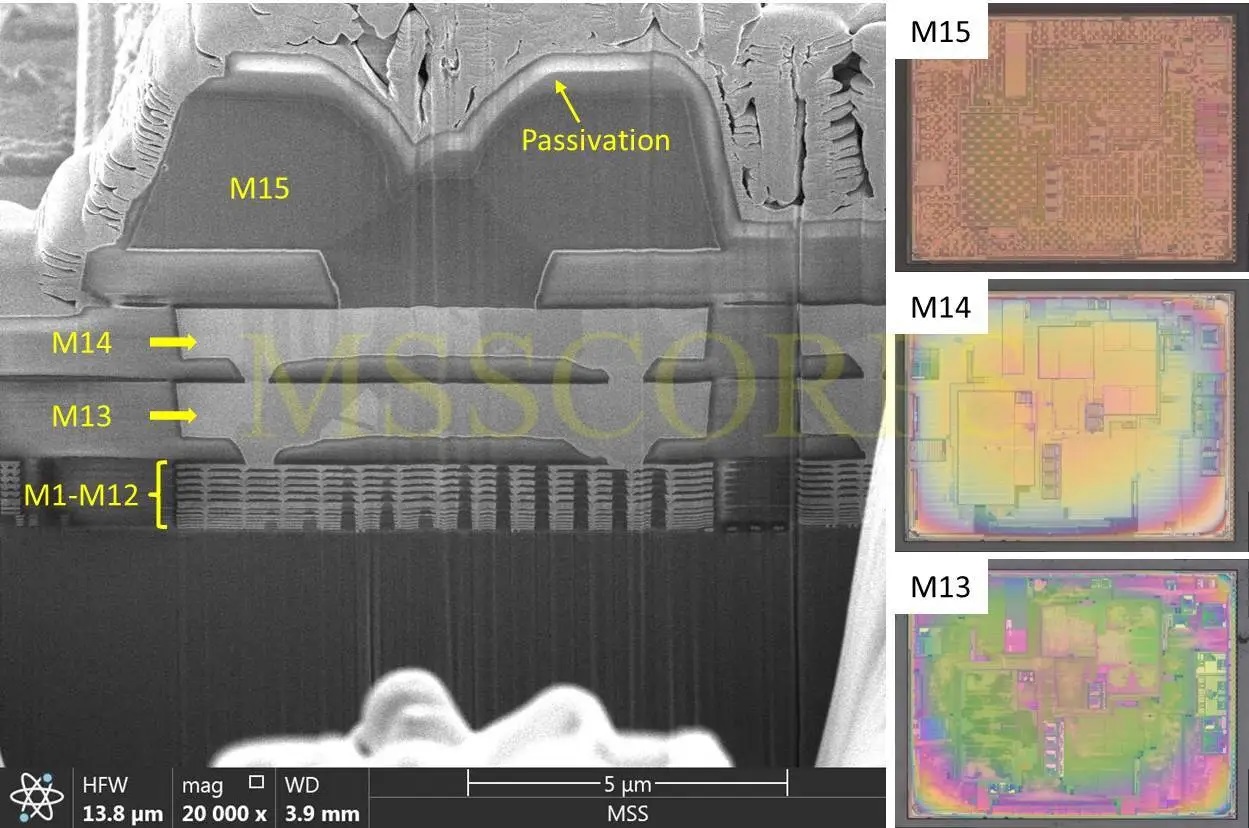

欲了解Exynos W1000製程的第一步,可以由聚焦離子束截面(Focused ion beam cross-section;FIB CS)分析開始,圖2左側大圖為晶片的截面圖,由圖中可以清楚看到Exynos W1000的製程為一層保護層(Passivation layer)加上15層金屬層,其中最上層的金屬層(M15)也就是重佈線層(Redistribution layer;RDL),除了由截面分析獲得Exynos W1000的初步製程資訊,透過逐層的平面去層(Parallel mapping)可以了解各金屬層的佈局(Layout)。

圖2:上方大圖為Exynos W1000截面聚焦離子束分析截面圖,右側分別為M15、M14、M13的光學顯微鏡圖。

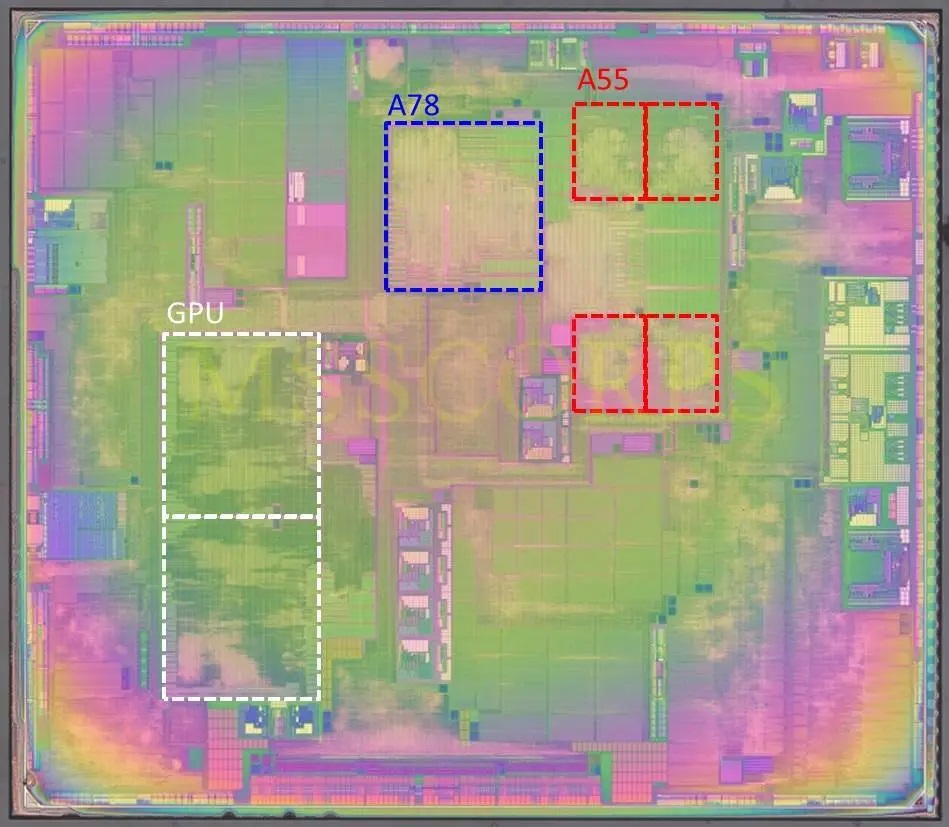

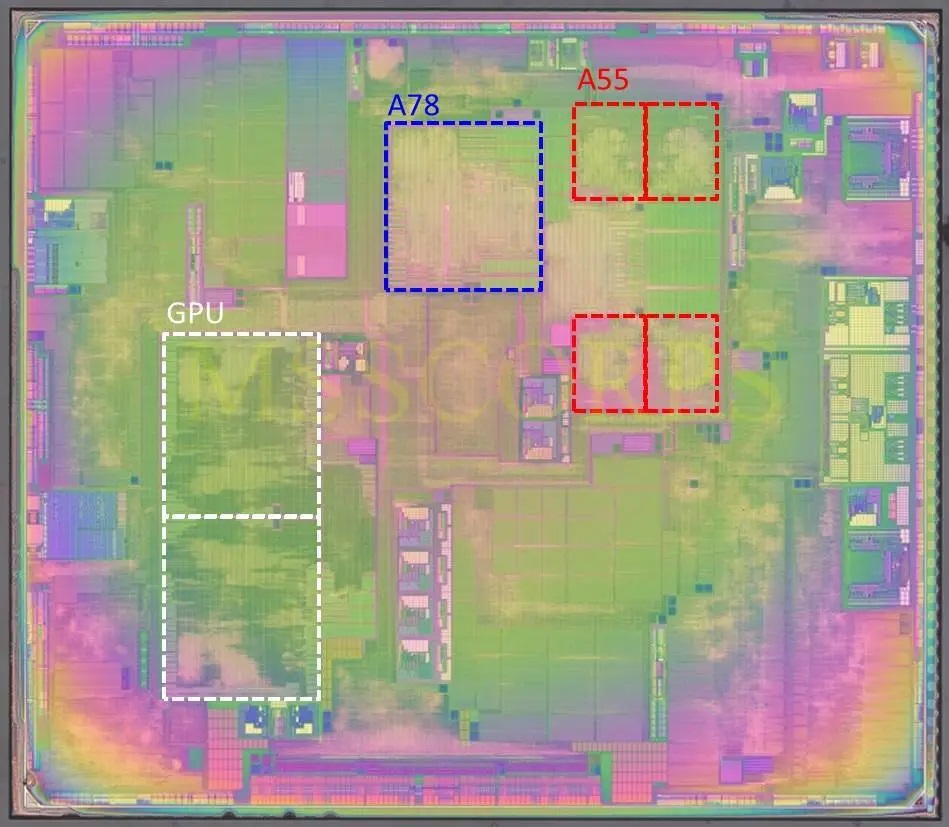

圖2右側顯示利用全平面去層技術,將Exynos W1000由M15處理到M13的光學顯微鏡圖。根據三星官網的資訊,Exynos W1000有一個高效能的大核心CPU,Arm Cortex-A78與4個小核心CPU,Arm Cortex-A55,GPU部分則是雙核心的Arm Mali-G68 GPU,這些主要的CPU與GPU核心位置分別以不同顏色的虛線方框標示於圖3中。

圖3:M13光學顯微鏡圖,CPU與GPU分別以不同顏色虛線方框表示,A78為Cortex-A78,A55為Arm Cortex-A55,GPU為Arm Mali-G68 GPU。

Exynos W1000是第一個用於一般消費性產品採用GAA架構的微處理器,到底這新的架構與目前主流的鰭式架構有甚麼差異?讓我們利用最先進的TEM與分析技術解開它的神秘面紗。

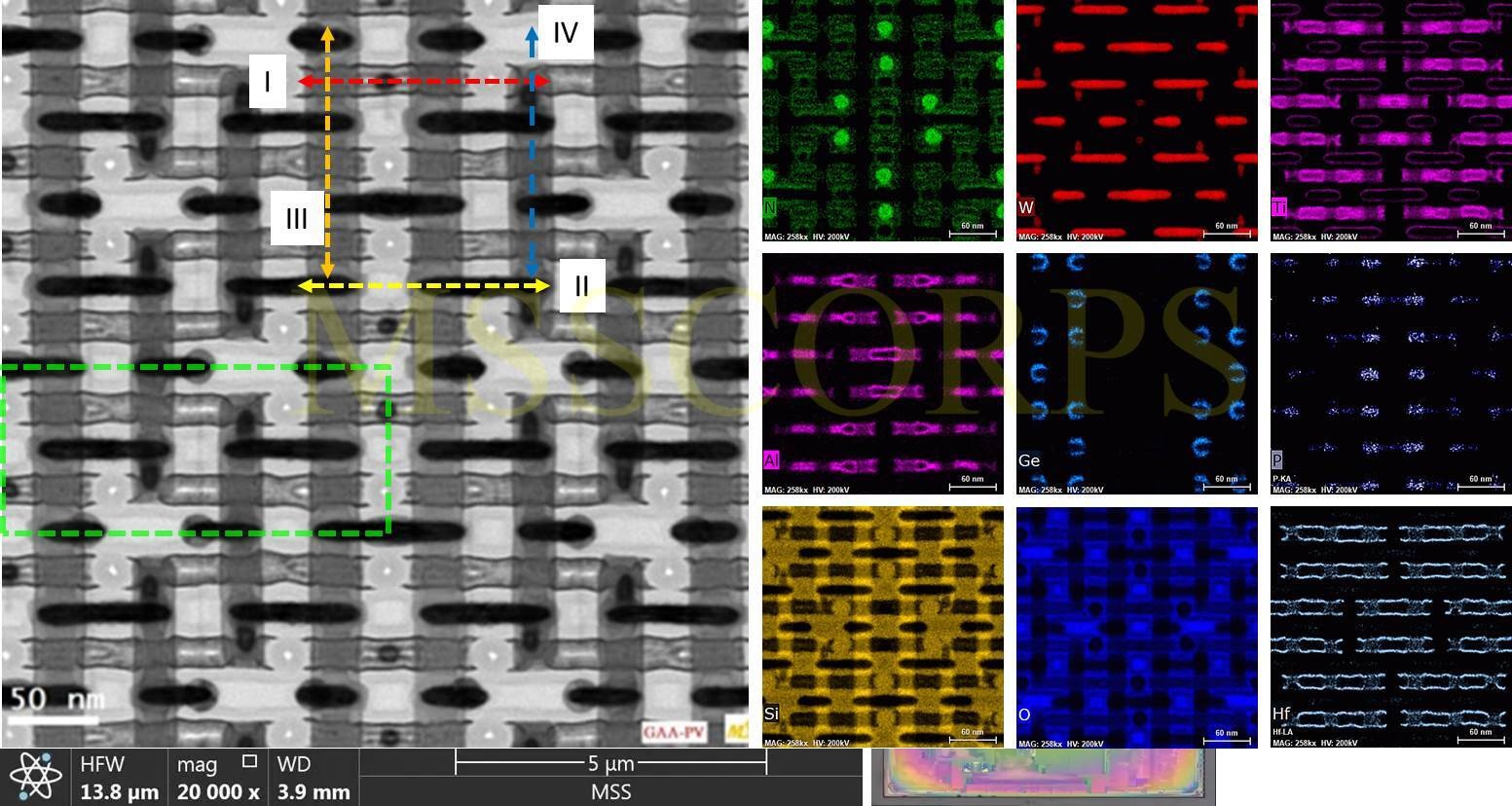

進行分析的位置是每個微處理器都會有的6T-SRAM區域,圖4左側大圖是6T-SRAM的平面穿透式電子顯微鏡(PVTEM)照片,6T-SRAM是由六個電晶體所構成,包含兩個PMOS與四個NMOS,其記憶體單元由綠色虛線方框標示,藉由EDS mapping分析(圖4右側小圖),可以獲得組成元素的分佈圖,並由分析的結果顯示,三星新一代的GAA架構並未出現有別於先前三星FinFET 4nm鰭式架構的新元素。

圖4:左側大圖為6T-SRAM平面STEM圖,單位胞由綠色虛線方框標示,I, II, III, IV分別為XTEM的分析方向,I方向為Along Gate,II方向為Along S/D,III方向為Along N-GAA,IV方向為Along P-GAA,右側小圖為左側大圖各個元素的EDS Mapping分析結果。

由於GAA架構較為複雜,平面加上截面觀察才能完全顯現其3D結構,因此我們分別在四個方向(圖4左側大圖內以I、II、III、IV標示)以截面穿透式電子顯微鏡(XTEM)分析GAA架構的細節。

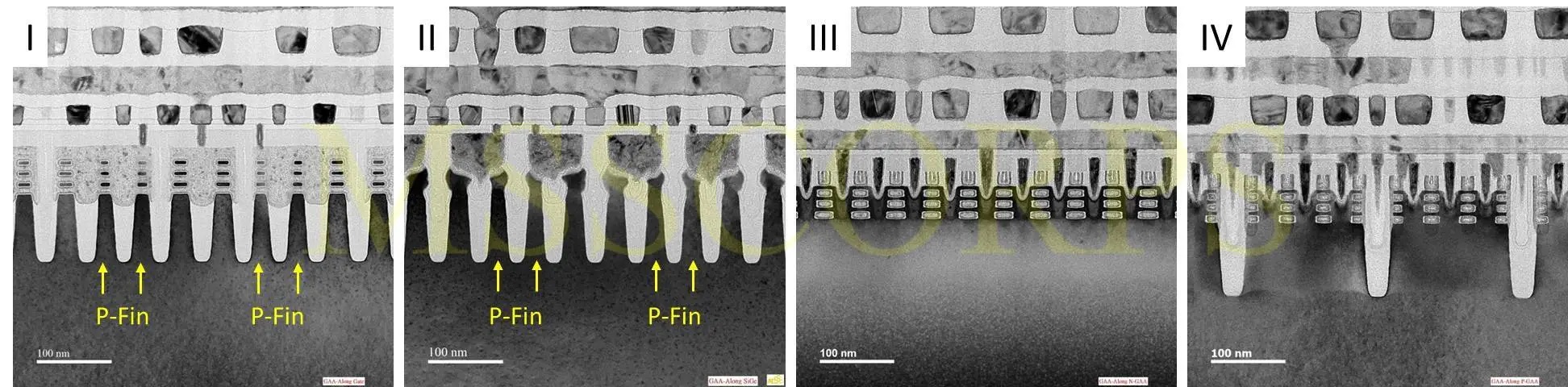

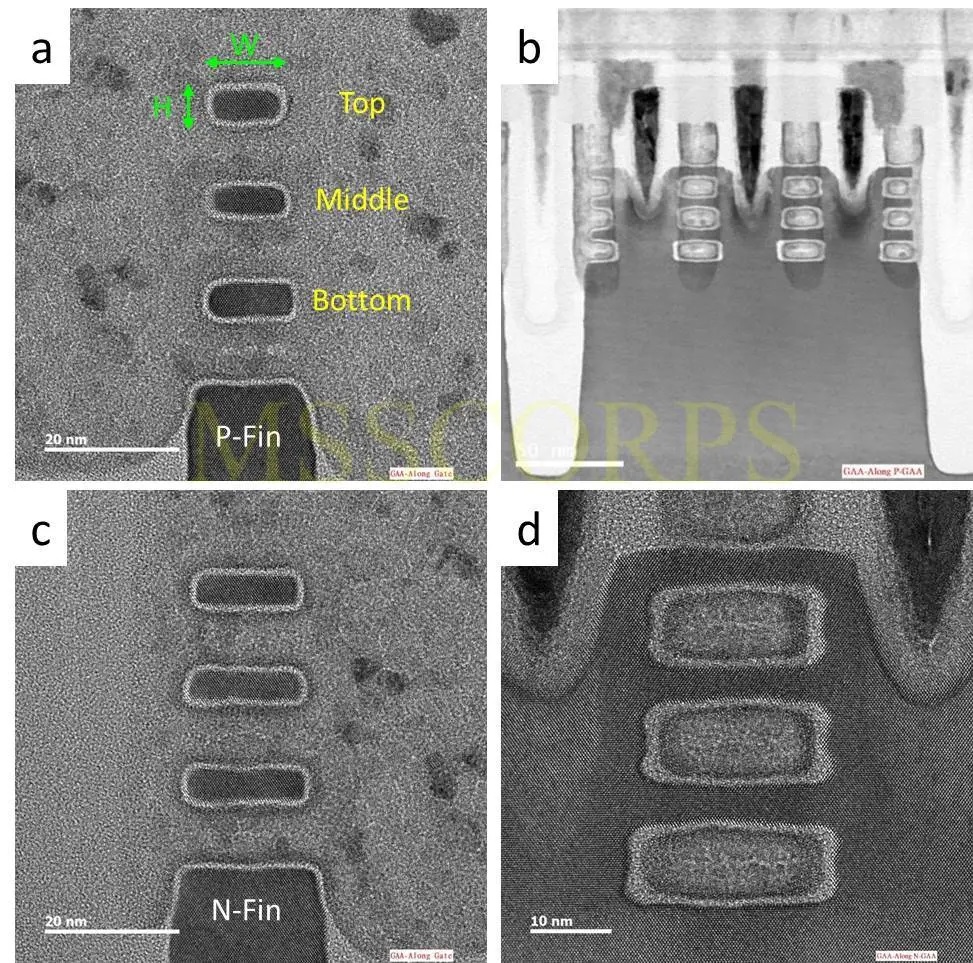

圖5為這四個方向的XTEM照片,由圖5I可以清楚的看到無論是P-Fin或是N-Fin上方都有三個通道,通道側邊可以由圖5III & IV觀察到通道四方完全被閘極所環繞,這與先前發表的三星鰭式架構TEM照片有很大的差異。

圖5:XTEM圖,分析方向為沿著圖4左側大圖所標示的四個方向,黃色劍號標示為P-Fin位置。

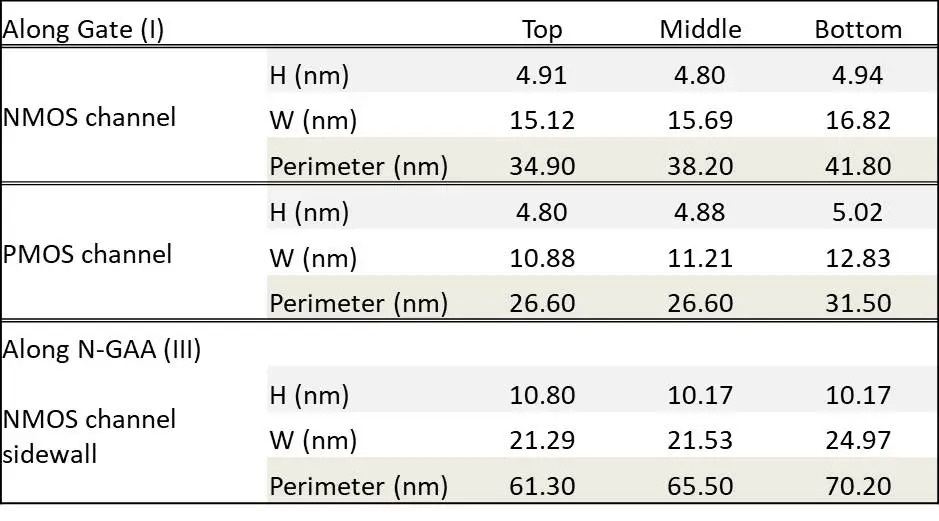

通道的數量與截面積都是決定電晶體在作動時能夠乘載多大電流的關鍵參數,由高解析的TEM照片(圖6)可以獲得更多GAA架構細節,圖6a與c清楚地顯示P-Fin與N-Fin在I方向(Along gate)上的通道截面積有明顯的差異,N-Fin上的通道截面積明顯比P-Fin上的通道截面積大,而由III (Along N-GAA,圖6b)與IV(Along P-GAA,圖6d)方向的TEM照片結果顯示,P-Fin與N-Fin上的通道側邊面積大小並沒有明顯差異;表1整理與通道相關的關鍵尺寸。

圖6:(a & c)分別是PMOS與NMOS沿著I方向在通道位置的TEM放大圖,W & H定義為通道寬度與高度的關鍵尺寸;(b) PMOS沿著IV方向在通道側壁位置的TEM放大圖;(d) NMOS沿著III方向在通道側壁位置的TEM放大圖。

表1:通道關鍵尺寸量測表,量測位置標示於圖6a。

表1:通道關鍵尺寸量測表,量測位置標示於圖6a。

由PVTEM與XTEM照片可以清楚知道,相較於鰭式架構,GAA架構在製程上的複雜度與困難度都高出許多,也導入了多項新的製程,包含磊晶成長(SiGe/Si epitaxy;S/D epitaxy)、蝕刻(Fin reveal、cavity etch、NW release)…等等。由於製程節點已來到只有數奈米級,為了讓電晶體能夠發揮最佳效能,製程要求的規格已經到了原子級的嚴謹程度,多一排或少一排原子最後都會造成電晶體在效能上的差異或甚至失效。

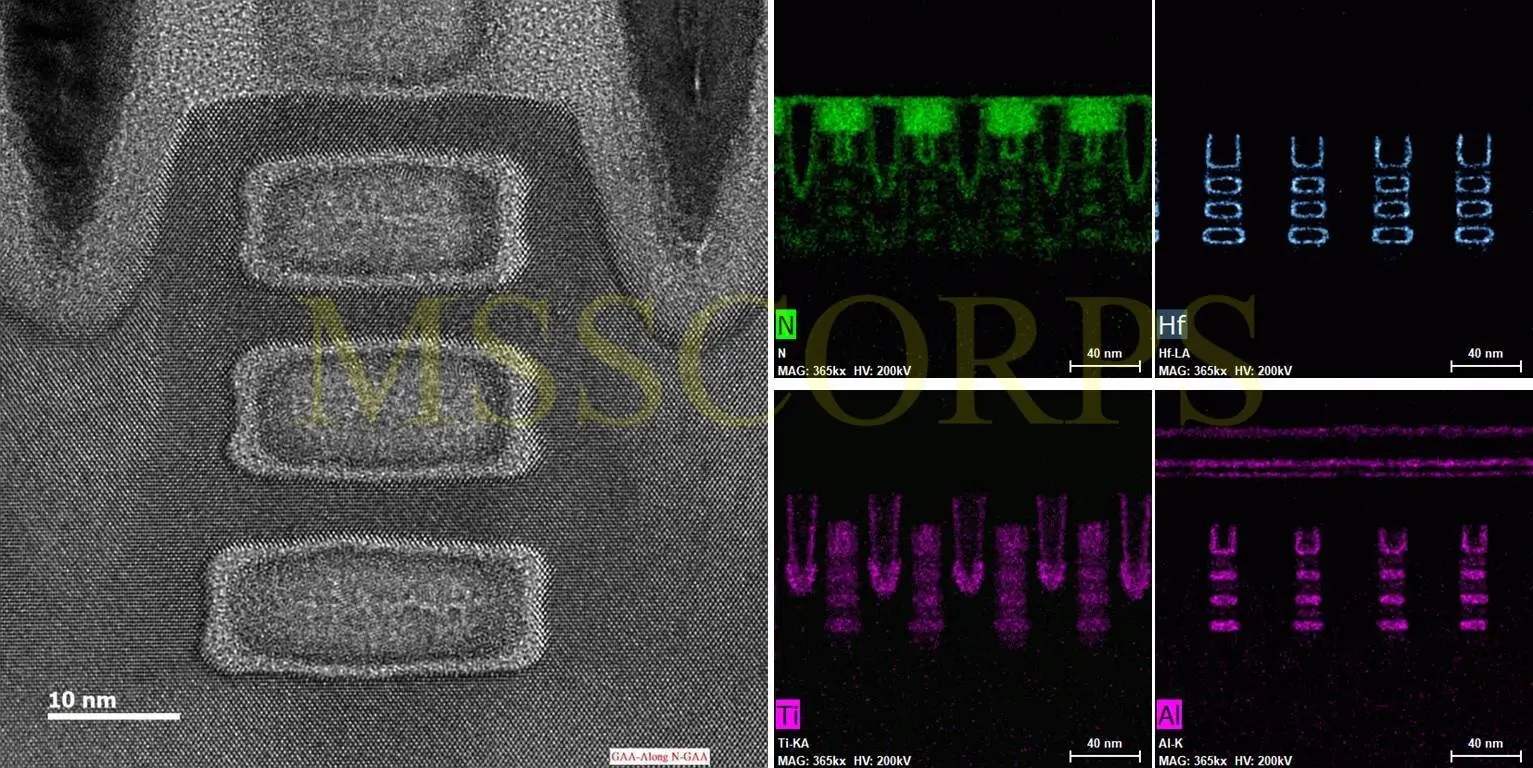

以電晶體最重要的電性參數之一——「臨界電壓」(Threshold voltage;Vth)為例,臨界電壓是閘極控制通道電流開(“1”)與關(“0”)的關鍵,實務上,臨界電壓越小越好,臨界電壓的大小與閘極/通道之間功函數(Work function)的差異有正相關,而功函數的差異與材料的特性與堆疊品質有關。為了精準地控制功函數的差異,閘極/介電層/通道堆疊結構的介面平整度就扮演了相當重要的角色,由圖7左側大圖可以清楚看到GAA堆疊與介面平整度的狀況,右側小圖為部分元素的EDS Mapping,可以了解高介電材料與閘極的組成元素的分佈狀況。

圖7:左側大圖為NMOS沿著III方向在通道側壁位置的高解析TEM圖,右側較小倍率的小圖為其中四個元素(N, Hf, Ti, Al)的EDS Mapping分析結果。

綜合上述的結果與說明可知,製程技術的創新是推進電晶體架構不斷演進的底氣,也是晶片整體效能能夠持續提升重要的驅動力,GAA並不會是電晶體架構的終點;因應越趨複雜的製程架構、多樣的材料以及原子等級的結構尺寸,材料分析也必須與時俱進,以獲得精準的實驗結果。