EETIMES 刊登 汎銓科技技術文章 電晶體世代交替由FinFET到GAAFET

![]() 2024.11.6

2024.11.6

新聞公告

新聞公告

為了更直觀地了解FinFET到GAAFET架構世代的差異,本文利用高倍率的電子顯微鏡影像進行深入的探討與分析,觀察其於結構微觀層面上的特徵...

電晶體自1947年在貝爾實驗室誕生以來,標誌著人類電子工程技術的新時代。電晶體進入量產階段後,隨著技術的不斷進步,其密度以每兩年的速度倍增,不斷提升晶片的性能與功能,這也就是著名的「摩爾定律」。

電晶體的基本組成部分包括基板、閘極、源極與汲極,其中,閘極位於源極與汲極之間,且與基板之間隔著一層絕緣層,電流通過通道自汲極流向源極,而電流是否導通則取決於施加在閘極上的電壓,這一設計讓電晶體能夠有效地開關電流,成為現代電子產品的核心元件。

隨著先進製程的不斷微縮,為了增強閘極對通道的控制能力並降低漏電,電晶體的架構從傳統的2D結構演進至3D的FinFET架構,FinFET架構的引入,顯著增強了閘極對通道的控制並減輕短通道效應,提供更佳的功耗和效能優勢。到了2023年,電晶體架構進一步演變為GAAFET,在GAAFET架構中,閘極以四個方向完整包覆通道,提供了更佳的控制能力,使其在面對更嚴峻的製程挑戰時電晶體仍然能穩定地提升其性能。

儘管GAAFET架構看似複雜,但有研究文章指出,GAAFET架構在製程上仍有很大一部分沿用原有的FinFET架構的製程,降低了晶圓代工廠在GAAFET架構的製程研發上所面對的技術挑戰。

為了更直觀地了解這兩種架構的差異,本文將利用高倍率的電子顯微鏡影像進行深入的探討與分析,希望透過這些高解析度的影像,清晰地觀察到這兩種架構在結構微觀層面上的特徵,讓讀者能對電晶體的架構及其技術上的變革,能有更深刻的認識與理解。

在接下來的文章中,我們將展示這兩種電晶體架構的電子顯微鏡影像,以及對其結構的詳細解讀,帶領讀者深入了解電晶體技術的演變及未來的發展方向。我們這次比較的產品是Samsung S22與Samsung Galaxy Watch 7,Samsung S22的應用處理器為Exynos 2200,使用的是Samsung 4nm FinFET製程節點,Samsung Galaxy Watch 7的應用處理器為Exynos W1000,使用的是Samsung 3nm MBCFET製程節點,其中MBC為Multi bridge channel的縮寫,就是閘極環繞整個通道的架構,也就是GAA架構。

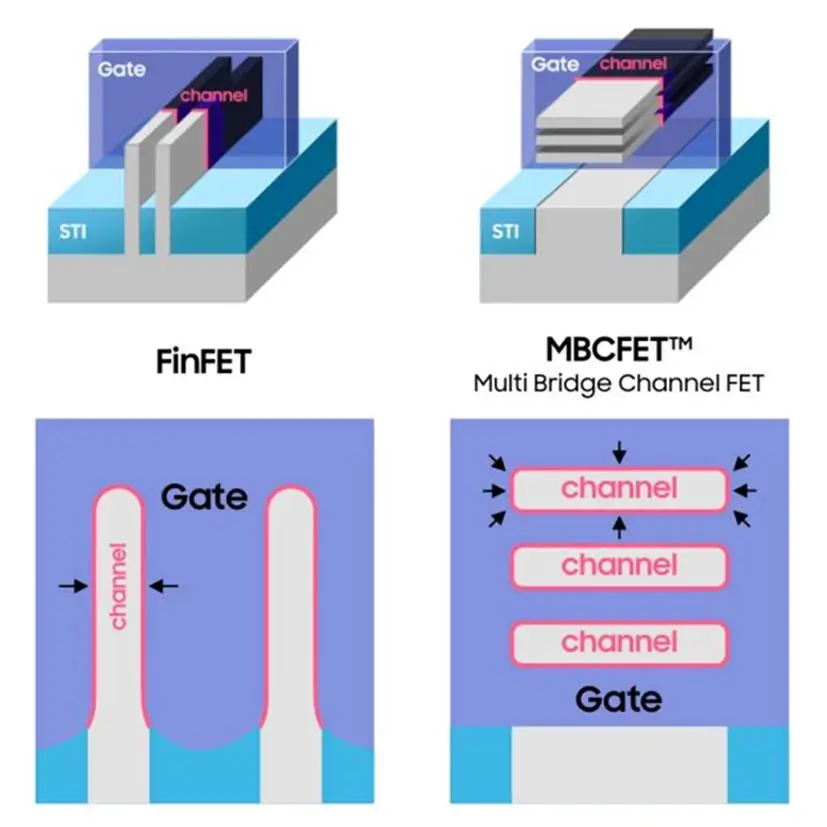

由Samsung官網中所提供FinFET與MBCFET的動畫圖(圖1),可以清楚的了解到這兩種電晶體架構的差異最主要是在閘極的結構,FinFET架構中的閘極是將通道三方包圍,而MBCFET的通道四面則是完全被閘極所包圍。

圖1:FinFET與GAAFET電晶體架構動畫圖。(來源:https://semiconductor.samsung.com/news-events/tech-blog/3nm-gaa-mbcfet-unrivaled-sram-design-flexibility/)

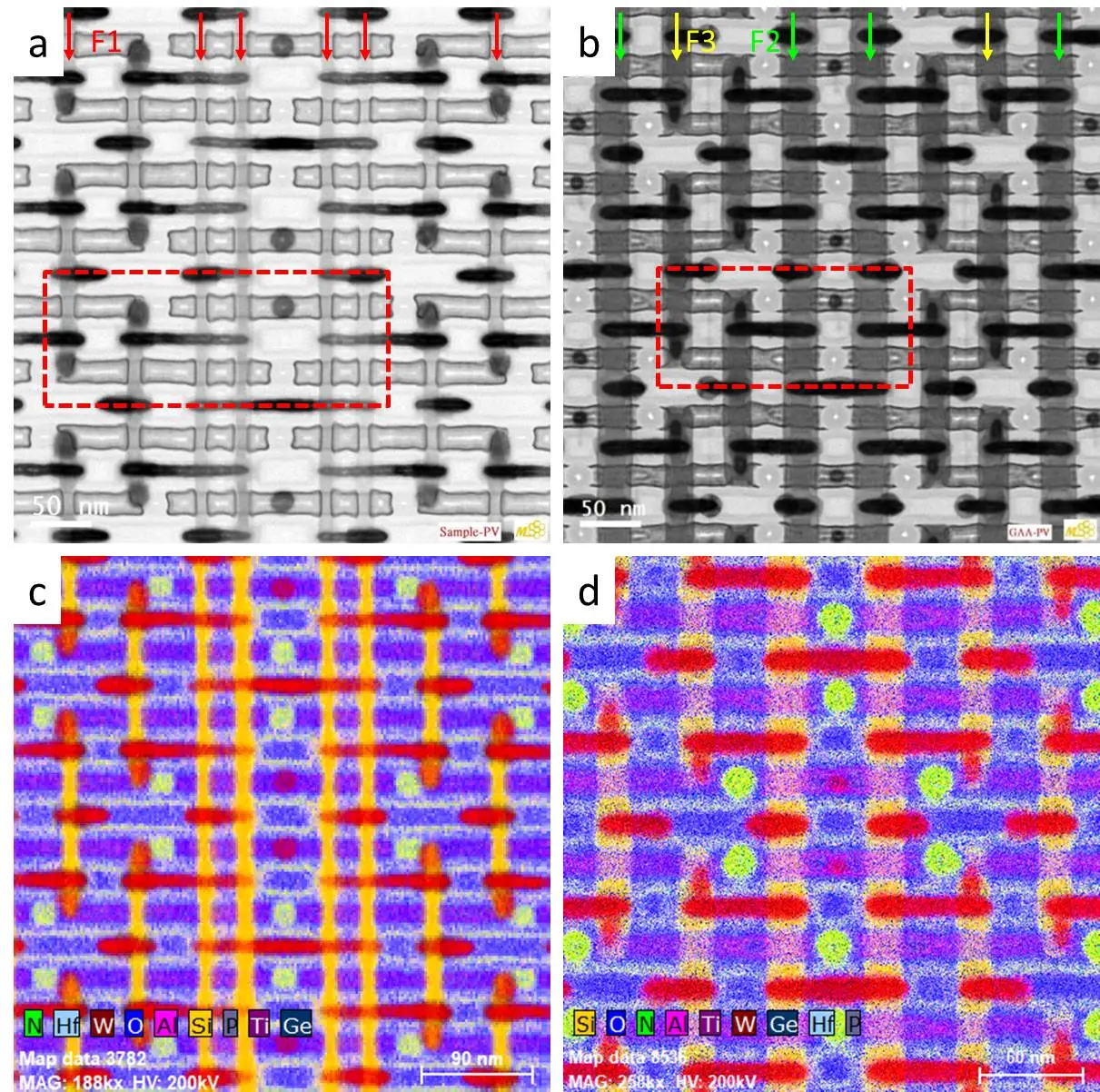

圖2a&b分別是4nm FinFET與3nm MBCFET的平面掃描穿透式顯微鏡的影像,分析的位置都在其應用處理器的6T-SRAM區域,由圖中我們可以清楚看到Fin(以紅色、綠色、黃色箭號標示)是沿著縱軸(Y)的方向排列,Fin的寬度則有明顯的差異,FinFET (圖2a)中的Fin的寬度最窄,N-Fin與P-Fin的寬度並沒有發現有明顯的差異,以紅色F1標示,而MBCFET (圖2b)中的Fin則明顯寬很多,且寬度可以分成兩種,分別以綠色F2與黃色F3標示,這剛好與通過的電晶體型態有直接關係,最寬的Fin(F2)通過的是NMOS,而次寬的Fin(F3)通過的是PMOS。

我們將6T-SRAM的單元用紅色虛線方框標示發現,4nm FinFET與3nm MBCFET架構在其單元內分別包含6根與4根Fin,而在橫軸方向都是包含兩個多晶矽閘極(Poly gate),為了解製程的微縮程度,一般讀者都會有興趣比較前後代製程在關鍵尺寸(CD)的差異,例如多晶矽閘極間距(Poly pitch)、鰭片間距(Fin pitch)…等,但因為我們分析這兩個6T-SRAM的區域並非在同一功能區塊,在此只能就製程的細節做討論,無法比較相關的關鍵尺寸。

新一代電晶體在架構上有了革命性的改良,為了使其有更好的效能,通常在製程上也可能會導入新材料,我們利用EDS Mapping來分析這兩種電晶體架構的元素分佈,由圖2c&d的結果我們可以清楚了解在EDS分析的解析度下,4nm FinFET與3nm MBCFET在元素分佈上並沒有明顯的差異,如果需要確認兩者之間的微小差異,我們就必須借重解析度更高的分析工具。

圖2:(a) Samsung 4nm FinFET掃描穿透式電子顯微鏡影像,Fin以紅色箭號標示(F1);(b) Samsung 3nm MBCFET掃描穿透式電子顯微鏡影像,Fin以綠色(NMOS)與黃色(PMOS)箭號標示(F2&F3)。6T-SRAM單元以紅色虛線方框標示,(c)&(d) 分別為(a)&(b)的EDS Mapping。

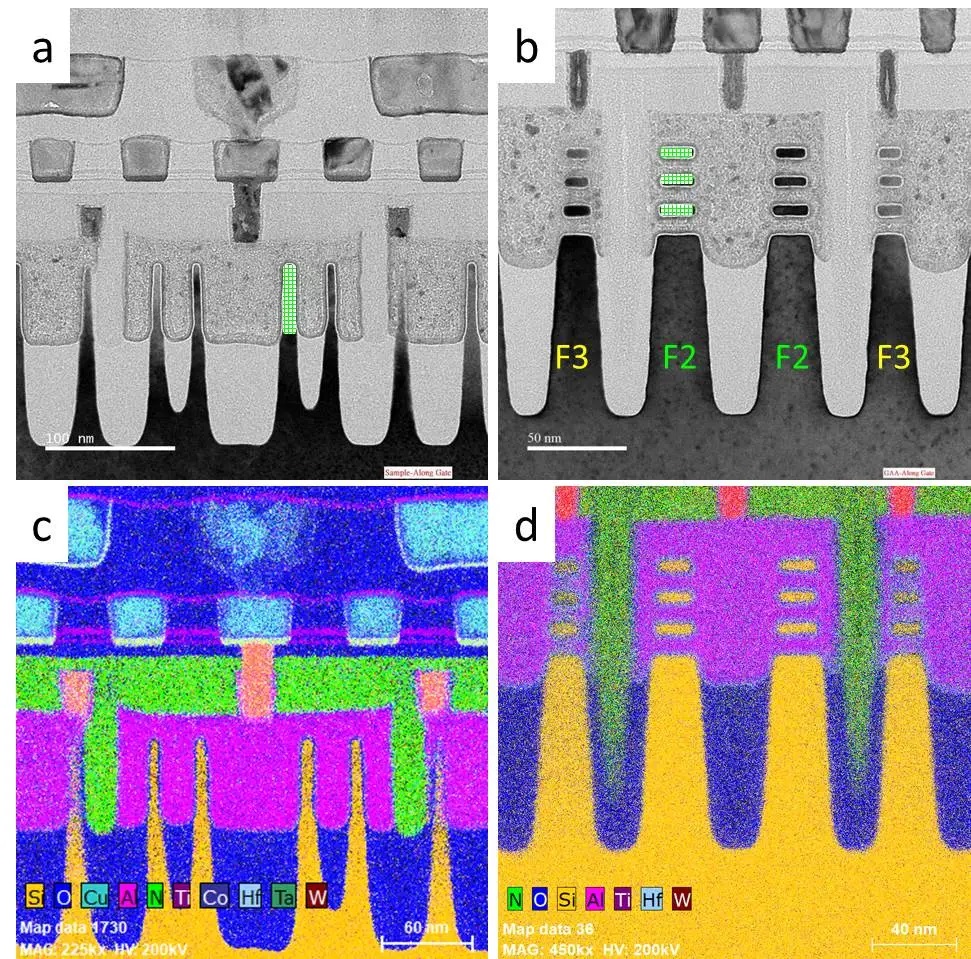

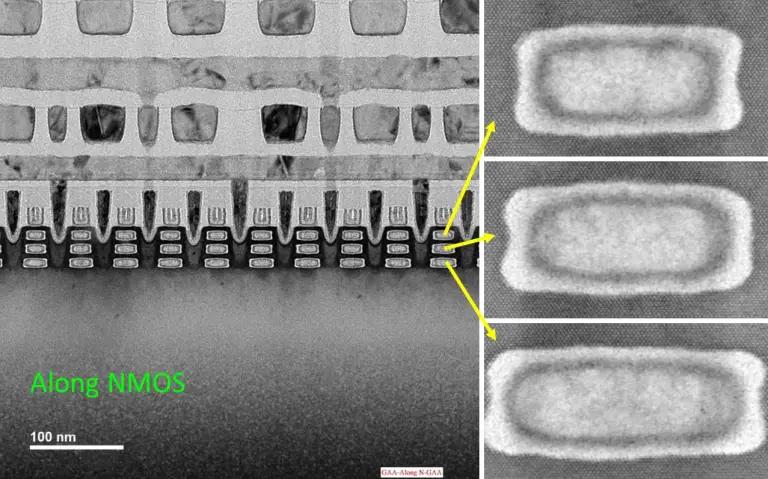

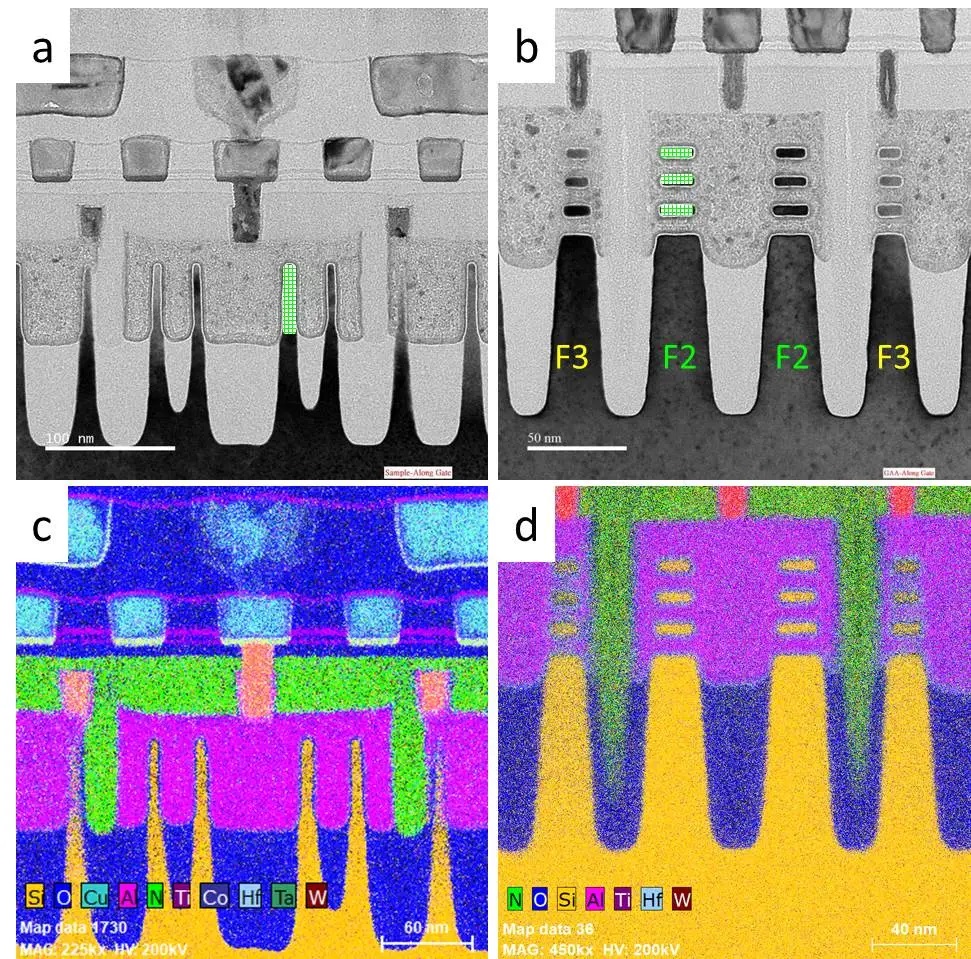

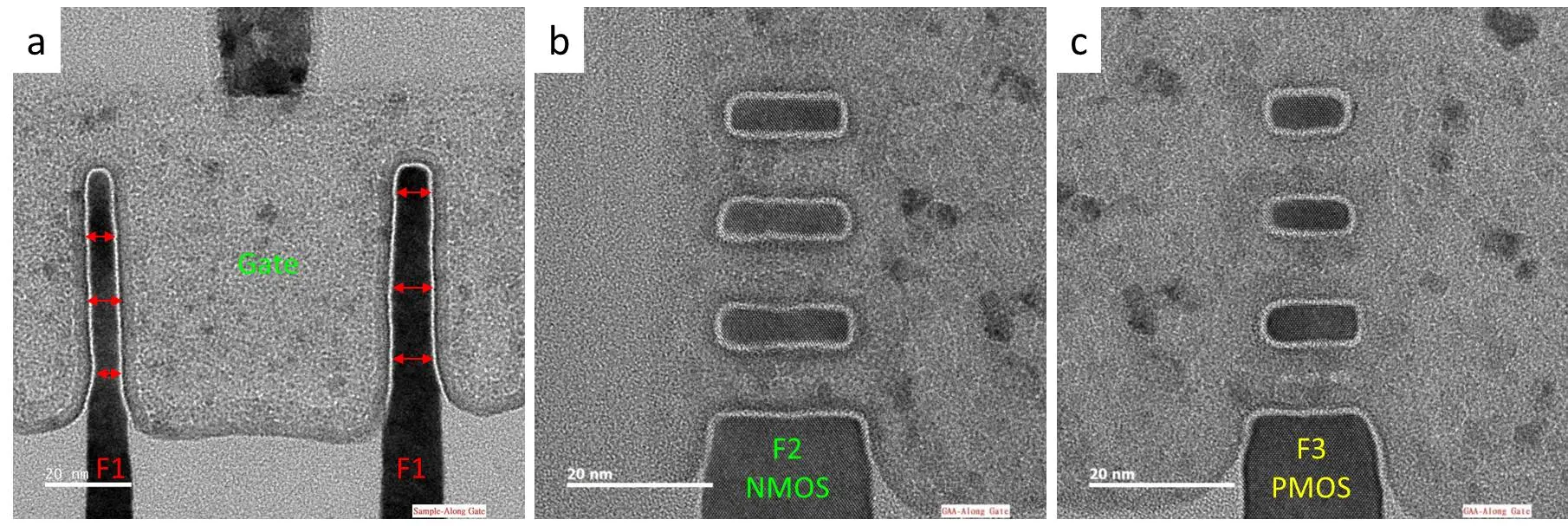

平面搭配截面穿透式顯微鏡的分析才能完全呈現3D電晶體的形貌,圖3是4nm FinFET與3nm MBCFET的截面穿透式顯微鏡沿著Gate方向分析的影像,這個方向剛好可以讓我們清楚觀察Fin的形貌與通道的截面,通道的截面以綠色虛線方框標示,在FinFET的架構下,通道的截面是細長柱狀的結構,但寬度並不完全均勻,上面較寬,靠近閘極下方邊緣轉折處較窄,而MBCFET在每個Fin上方都有3個通道,通道截面為四角呈現圓弧的長方形形狀,稱為奈米薄片(Nanosheet)。

根據我們先前的分析,N-通道較P-通道寬,寬度分別約為16nm與11nm,高度都約為5nm,由圖3a&b的截面觀察方向我們也可以清楚觀察到這兩種架構在Fin與通道在寬度上的差異,這與圖2在平面方向的觀察是一致的,另外,我們也將Gate方向的截面利用EDS Mapping來分析這兩種架構組成元素的分佈情形,其結果呈現在圖3c&d。

站在晶圓代工廠的立場,研發新的電晶體架構製程顯然比沿用已經成熟穩定的製程,就資本支出上一定高出許多,且存在許多風險,因此都會傾向以不變應萬變,繼續沿用原來架構的製程,直到碰觸到再也無法提升效能或衍生致命性問題的情形。

圖3:(a)&(b) Samsung 4nm FinFET與Samsung 3nm MBCFET沿著閘極方向的穿透式電子顯微鏡影像,其中一通道截面以綠色斜線方框標示。(c)&(d)分別為a&b的EDS Mapping。

FinFET電晶體架構在2012年正式量產後,製程節點由22nm推進到3nm,歷經12個年頭已接近尾聲,全球主要先進晶圓代工廠一致認為3nm以下會改由GAAFET架構接棒,其改絃易轍的原因主要是來自於FinFET天生架構的限制,考量電晶體的特性/效能有三大因素,分別是閘極的控制力、電容、以及乘載電流。

隨著製程的微縮,要有好的閘極控制力就必縮小Fin的寬度,要減少電容就必須縮減鰭片間距,要增加乘載電流就必須提高Fin的高度,然而由4nm FinFET的影像來看(圖2a),要進一步縮減/提高Fin的寬度/高度在蝕刻(Etching)與切割(Cutting)上面臨了極大的困難與技術挑戰,且當提高Fin高度的同時,卻會衍生出寄生電容問題。

另一方面,Fin的數量都會是整數,在不提高Fin的高度下,為了增加乘載電流以提升效能就必須在標準單元內再增加一或兩個Fin,而增加的Fin就一定會占有面積,如此做法則會導致標準單元不但沒有微縮反而還增大,背道而馳,綜合上述說明可以清楚了解FinFET架構在走到3nm製程節點後,為了讓製程持續微縮、電晶體的效能持續提升,就必須以新的架構取代FinFET,考量到現有FinFET製程的相容性,很自然地,GAAFET架構便油然而生。

圖4:(a) Samsung 4nm FinFET在通道附近的局部放大圖,紅色雙箭號分別標示fin的通道寬度,(b)&(c) Samsung 3nm MBCFET在N&P通道附近的局部放大圖,分析方向:沿著閘極方向。

Samsung 3nm MBCFET架構就是改良了上述FinFET架構所面臨的問題,我們用較高解析度的影像來比較兩種架構的形貌,FinFET (圖4a)的通道寬度有寬有窄,形狀較不規則,且閘極只有在三個方向包覆著通道,相反地,MBCFET (圖4b&c)架構的通道則是完全被閘極所包圍,因此有較佳的閘極控制能力,利用兩個垂直方向的截面電子顯微鏡分析,我們可以獲得MBCFET通道的3D結構。圖4b&c與圖5分別是沿著Gate與NMOS分析方向的影像,可以清楚觀察到通道截面與側面被閘極包覆的狀況是相當完整的,通道在截面方向(圖4a&b)的寬度也算均勻。

圖5:大圖顯示Samsung 3nm MBCFET沿著NMOS方向的穿透式電子顯微鏡影像;小圖則是上、中、下通道局部放大圖。

另外,MBCFET的奈米薄片還有另一項優勢,那就是其寬度可以在不增加標準單元的情形下,比FinFET更有彈性的調整空間,這由圖4a&b中MBCFET架構的通道寬度因為NMOS與PMOS的電性匹配而有兩種寬度得到印證,更重要的是,根據Samsung所發表的文章,MBCFET架構沿用90 %或甚至更多原本FinFET架構的製程,因此製程由FinFET轉變成MBCFET架構才得以順利完成。

個人行動裝置可以說是推動電晶體架構由平面轉為3D的主要驅動力,而由3D架構進入到埃米世代(A世代)將會是由有著海量需求的人工智慧(AI)所推動。根據先進製程研究機構imec的技術藍圖,GAAFET前後將會有兩個主要的架構,先是奈米薄片,接著是叉薄片(Forksheet),預計在2032年會開始導入互補式電晶體(CFET)架構,結合新穎的二維材料與創新的製程技術,CFET的標準單元將由GAAFET架構的5-6進一步縮小至4或甚至更小。可以說,從今年往後看至少10年,邏輯電晶體的發展是相當精彩可期,且讓我們拭目以待。