ESD靜電防護能力試驗

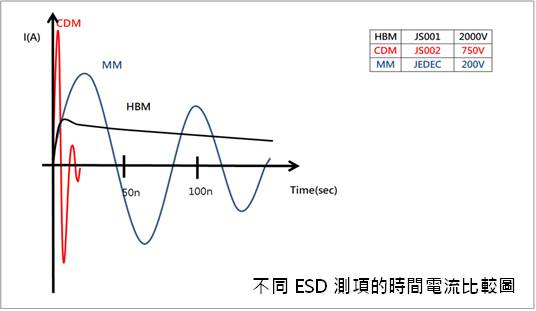

ESD靜電放電能力測試,在電子產品可靠度驗證前期電性驗證中,是非常重要的一環。靜電充斥在我們日常生活環境中,是一種自然產生的現象,尤其對於半導體產品使用的影響性更大。透過ESD靜電放電能力測試,以確認產品的抗靜電水準,有助於使用者在設計應用時的保護機制與防護措施。汎銓科技領先購置ThermoFisher最新型ESD測試設備,除大幅改善舊型設備的高寄生電容問題外,軟體功能更加人性化。針對電子零件類的ESD靜電放電能力測試,目前提供的服務項目包括:人體靜電放電模式 (HBM,Human Body Model)、機械靜電放電模式(MM,Machine Model)、充電放電模式(Charged Device Model)等項目。此外,在模擬電子產品電性過壓測試(EOS,Electrical Over Stress)所採取的常溫與高溫閂鎖測試(LU,Latch-Up),也是非常重要的測試項目。

– I-V Curve、HBM、MM與CDM

– Latch-Up

閂鎖測試(Latch-Up)是CMOS技術所特有的寄生效應,嚴重者會導致電路的失效,甚至燒毀晶片。當發生強電場施加在晶片氧化物薄膜,造成擊穿損壞,並由於浪湧電流造成的過熱而形成開路,產生所謂的“閂鎖效應”。當閂鎖發生時,晶片電源與地之間形成短路,造成大電流、EOS(Electrical Over Stress)損壞晶片。Latch-up測試包含I-test/Over voltage(V-test)兩種,試驗溫度則有常溫(Class I)與高溫(Class II)兩類。下圖為高溫Latch-Up設置方式。

– ESD設備

- • MK.2TE:HBM最高8KV、MM最高可測2KV、Latch-Up最高可測30V/2A或是100V/1A,最多可同時獨立上電5組電源、768測試腳位。

- • MK.4TE:HBM最高8KV、MM最高可測2KV、Latch-Up最高可測100V/18A,最多可同時獨立上電7組電源,共有2304測試腳位。

- • Orion3:CDM測試最高可輸出2KV,並可進行6GHz波形(Waveform)量測,採用Non-Socket方式進行測試,最大可測試樣品6.5cm x 6.5cm,可用測試探頭包含:ESDA / JEDEC / CCDM /JS-002等。

- • ESD測試公板:除BGA各類pitch公板外,同時提供超過五十種以上的封裝種類公板,可隨時支援客戶所需。

▍技術與排程服務窗口

ESD:陳先生

+886-3-6663298 ext. 3999

esd@msscorps.com